# ECAL EUDET MODULE progress & perspective

EUDET annual meeting, oct, 18st, Munich

# Goal of the program

- Mechanic

- Validate a full length structure

- Validate fastening

- Validate thermal calculation

- Silicon sensor

- Validate physical behaviour

- Validate costing and production feasibility

- Electronic

- Validate front-end ASIC

- Ultra low comsumption

- o System on chip

- Daisy chaining and data outputting

## **EUDET** module overview

- Full length structure

- 500kg radiator

- 40k channels (1.3M if fully equipped)

# Mechanical R&D

On behalf of Marc Anduze & Denis Grondin LLR/LPSC

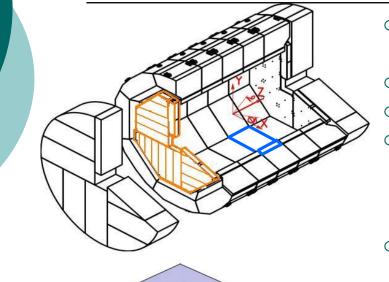

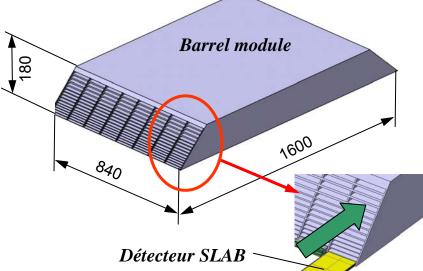

# ECAL for LDC- Global presentation

- W/Si calorimeter (24  $X_0$  with 29 W layers)

Weight full ECAL:  $\sim 112 \text{ T} (80 \text{ barrel} + 32 \text{ End-Cap})$

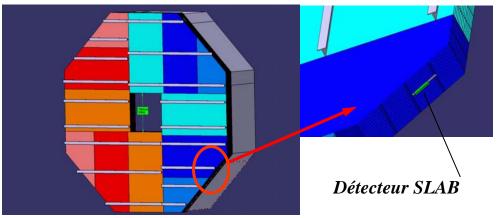

- Barrel: 40 identical trapezoidal modules

- End-Cap: constituted of 12 modules (3 types)

- ECAL module: alveolar structure carbone fibers compound including half of W plates (fixed on HCAL End-Cap with rails)

- Detection elements (detector slab) in each alveolar case (Si+W), FE chips integrated, pad size: 5×5 mm<sup>2</sup>

#### Multi-module End-Cap

# ECAL - Alveolar structure design

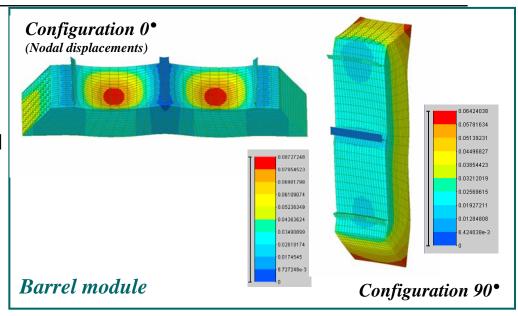

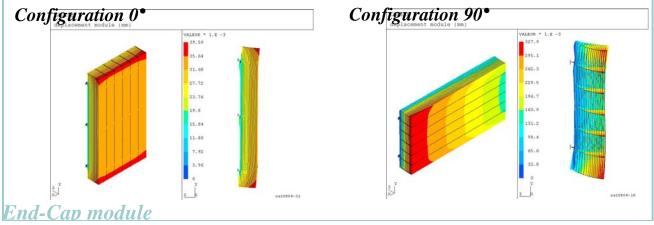

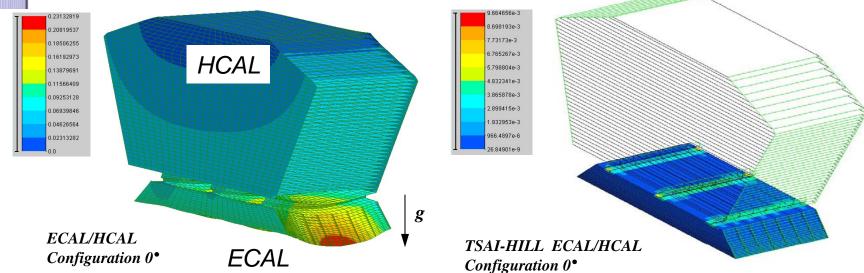

#### Linear Analysis

- Global simulations: global displacements and localization of high stress zone for different solutions (definition of dimensions)

- Local simulations: more precise simulations and study of different local parameters to design each part of theses structures

#### Main ISSUES:

Dead zones : thickness of main composite sheets

- Fastening system :

choice of fasteners

(metal inserts, rails...)

- Thermal cooling (active or passive ?)

- Connectors ?

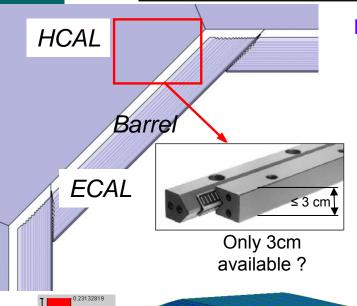

## **ECAL/HCAL** - Interface

Fastening system ECAL/HCAL is fundamental for mechanical and thermal calculations (barrel and End-Caps):

- choice of fasteners: rails directly inside composite

or metal inserts?

- Connections set path in gap between ECAL and HCAL (via a panel for cabling interface ?)

- Rails are 1 way for positioning system (gravity support) but a second complementary system may be added for fast interchange of modules... recommendation?

- Whole End-Cap (ECAL+HCAL) assembly behavior

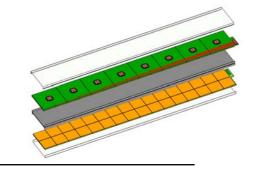

### **ECAL** - Detector slab

#### Main ISSUES:

#### Front End chips inside:

- ⇒ Thermal dissipation (cooling ?)

- ⇒ Chip behaviour in an electron shower (tests with a thin PCB in October 2006)

- Long structure :

- ⇒ Design and fabrication problems

(composite with segmentation of W plates, mechanical behaviour ...)

- ⇒ Segmentation of PCB (design of an interconnection)

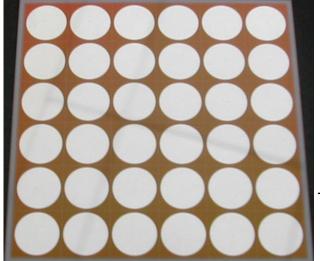

- Diminution of the pads size

- □ Increases of the number of channels (thermal cooling ?)

- ⇒ Size of glue dots

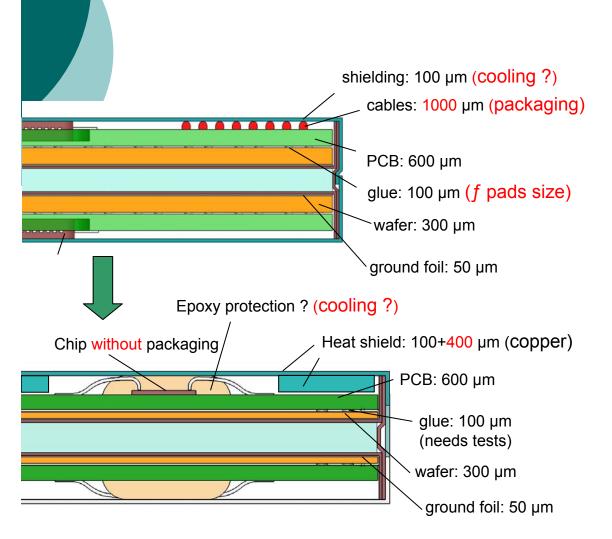

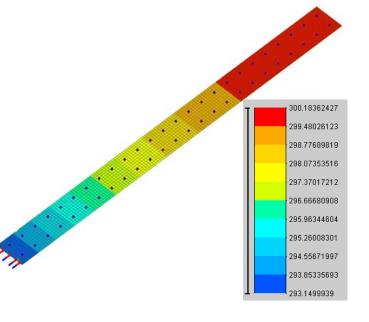

# ECAL - Thermal analysis

Thermal sources:

| Pad size            | Chan/<br>wafers | Ch/chip | Chip/wafer | Chip size<br>mm² | Chan/barrel | Chan/<br>End-cap |

|---------------------|-----------------|---------|------------|------------------|-------------|------------------|

| 5*5 mm <sup>2</sup> | 144             | 72      | 2          | 15x15            | 60.4 M      | 21.8 M           |

CALICE ECAL: ~ 82.2 M of channels

Assuming that the chip power is 25 µW/channel total power to dissipate will be : 2055 W

⇒ external cooling OK

#### inside each slab:

necessity of cooling system but active or passive?

Ex: Pessimist simulation of heat conduction just by the

heat shield :  $\lambda = 400 \text{ W/m/K (copper)}$ ; S = 124\*0,4 mm<sup>2</sup> L = 1,55 m ;  $\Phi = 50^* \Phi_{chip} = 0,18 \text{ W}$

We can estimate the temperature difference along the slab layer around 7°C and without contribution of all material from slab (PCB, tungsten, carbon fibers...)

⇒ passive cooling OK?

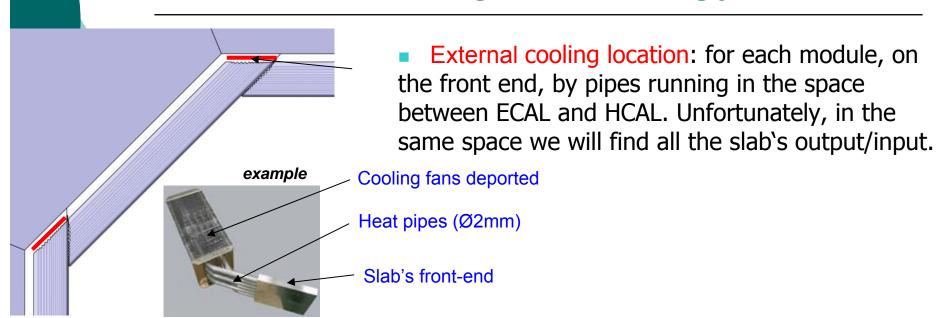

# ECAL - Cooling technology

- Nearly all heat generated by the chips will go to slab's front-end. Then, some cooling option can be foreseen:

- •Thermal conductors (heat shield) can be added in the slab to carry heat more efficiently along the slab direction.

- •Thermal cooling inside: by the way of heat pipes connected to cooling fans deported; increase the thickness of slab.

- Interest: thermal conductivity of heat pipe > 1000 times copper's one.

Heat pipes could "displace" the heat source in a busy place without energy source, without maintenance, at low cost. Heat pipe is only a means of transport for energy. (heat transfer is achieved thanks to a displacement of fluid)

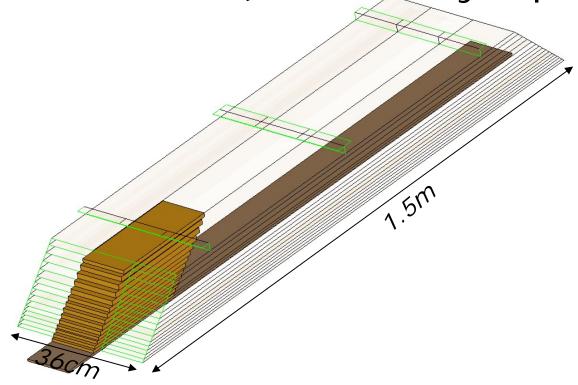

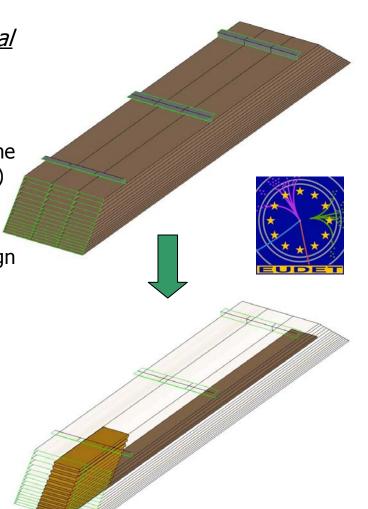

### **EUDET Module - Presentation**

# Concept : to be the most representative of the final detector module :

- A alveolar composite/tungsten structure with :

- same radiator sampling

- 3 columns of cells to have representative cells in the middle of the structure (with thin composite sheets )

- Identical global dimensions (1.5m long) and shape (trapezoidal)

- fastening system ECAL/HCAL (included in the design of composite structure)

- 15 Detector slabs with FE chips integrated

- 1 long and complete slab (L=1.5m)

- 14 short slabs to obtain a complete tower of detection (typ. L=30 cm?) and design of compact outlet.

# R&D – EUDET module (2006-2007)

- Long Type H structures :

- Design and fabrication of the long mould (end of 2006)

- Fabrication of validation model (1-3 samples )

- module EUDET:

- 1.5 m long ; ≈ 500 Kg

- real radiator sampling: 20 layers with 2.1 mm thick

9 layers with 4.2 mm thick

- Design (mechanical and thermal simulations) of the module

- Optimization of composite sheets: studies of main parameters (thickness, shape ...)

- Fastening system on HCAL: design and destructive tests too

- Design and fabrication of the mould with an industrial expertise (DDL consultants)

- Transport tools

- Fabrication of the structure (end 2007)

- Mechanical support for beam test in 2008

# R&D – Scope of work

Mechanical and thermal simulations:

**Linear Analysis**

- Global simulations :

- weight configuration: Barrel and End-Caps static study with external load (HCAL, LumiCAL ...)

- Nodal displacements: weakness of system mainly located on fastening points of modules hung on HCAL.

- Local simulations: more precise simulations and study of different local parameters to design correctly each part of this structure (thickness of main composite sheets, choice of fasteners ...)

#### Tests:

- Destructives tests to check local simulations

- Fastening systems and interface integration on composite structure

- Production specifications and moulds for long alveolar structure (Eudet)

#### **Medium-term perspectives:**

\_

- New calculation performed on each of module structures

- Finite Element Model of a HCAL/ECAL to estimate the overall deflection,

- Work to be done on the fastening systems (rails, facilitated insertion of modules)

- -Thermal analysis and technology: design and test of heat pipes connection to slab

- -Other cooling fluids (air, forced convection,...) to be studied if necessary.

# Silicon detector R&D

On behalf of Jean-Charles Vanel LLR

## Starting point: the physic prototype

- Several producer

- To manage production risks

- Russia

- Czech Republic

- Korea

- o Brazil

- o India

- Contact with Hamamatsu

Final detector : Cost driven

# Parameters change

| CALICE<br>Physic prototype | EUDET  |

|----------------------------|--------|

| Friysic prototype          | Wodule |

| Thickness       | 525μm  | 300µm  |

|-----------------|--------|--------|

| Pad size        | 1*1cm² | 5*5mm² |

| MIP in electron | 42000  | 24000  |

| Pad capacitance | 21pF   | 9.2pF  |

| Full depletion  | ~150V  | ~75V   |

- Still under study : Guard ring issues, leakage current

- Many data provided by test beams to be analyzed

- ECAL physic prototype analysis crucial for good detector optimization

# Electronic R&D

ILC\_PHY5

In behalf of : LPC/LAL/LLR/UCL

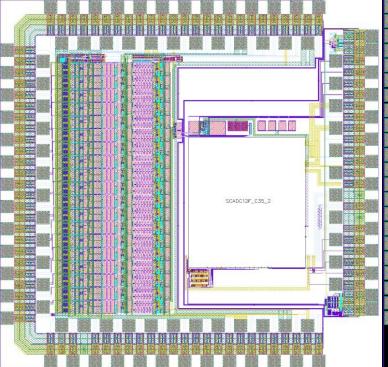

# System on Chip design

HaRD\_ROC (2006)

ILC\_PHY4 (2005)

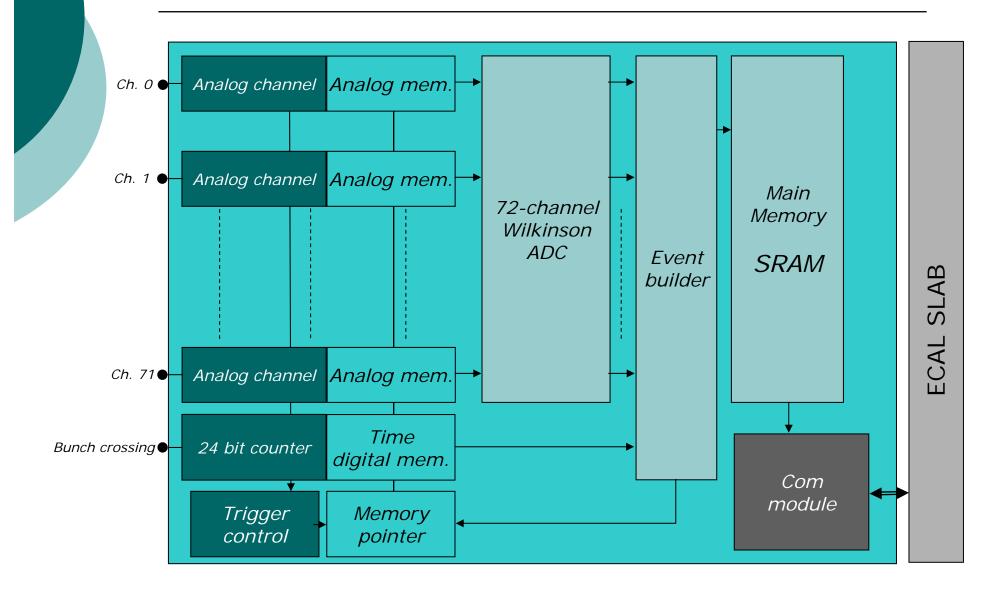

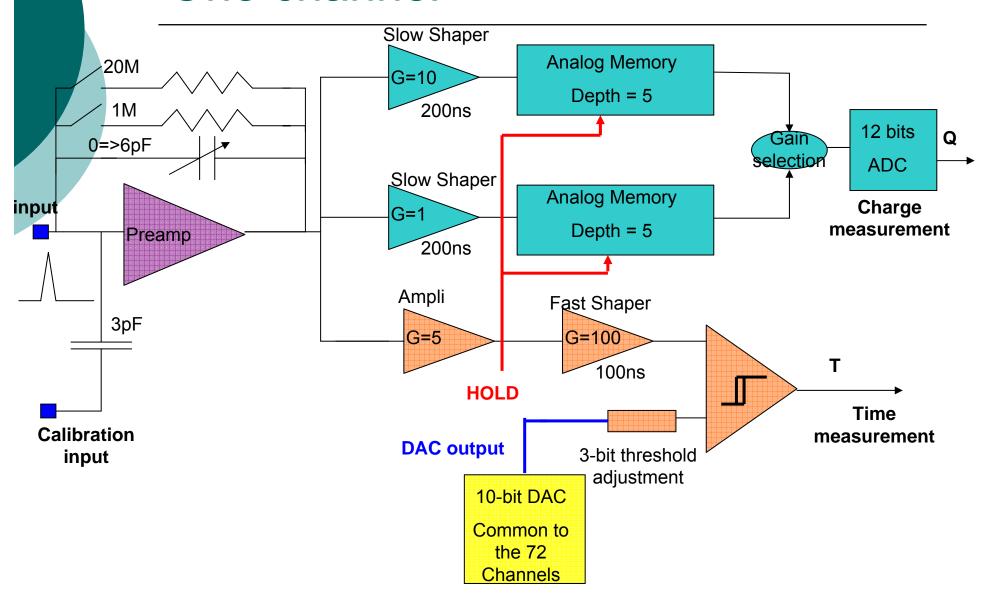

# Requirements for FEE

- Designed for 5\*5 mm² pads

- o 72 channels (first proto 36 ch.)

- Detector AC/DC coupled

- Auto-trigger

- 2 gains / 12 bit ADC → 2000 MIP

- Energy resolution : 4.89 GeV (cf JCB)

- 24 bits Bunch Crossing ID

- Internal SRAM with data formatting

- Output & control with daisy-chain

# Requirements for ILC\_PHY5 (contd)

- Power pulsing

- Programmable stage by stage

- Calibration injection capacitance

- Embedded bandgap for references

- Embedded DAC for trig threshold

- Compatible with physic proto DAQ

- Serial analogue output

- External "force trigger"

- Probe bus for debug

## General block scheme

## One channel

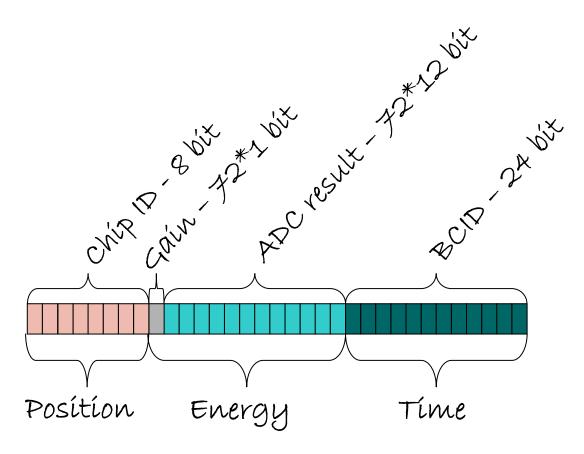

# One ILC\_PHY5 event

→ 968 bits / chip event

Depht is 5 because of room on silicon

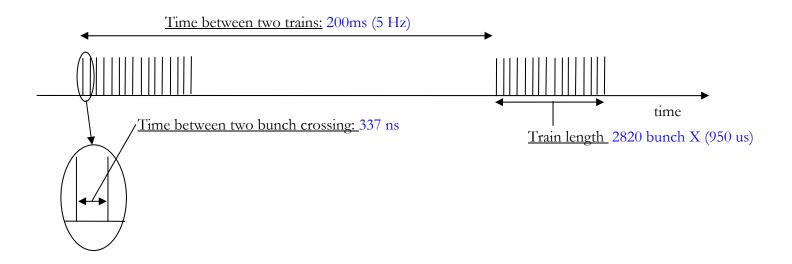

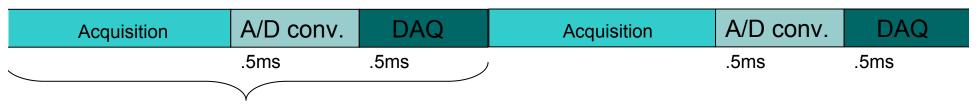

## Time considerations

| Acquisition | A/D conv.   | DAQ            | IDLE MODE   |

|-------------|-------------|----------------|-------------|

| 1ms (.5%)   | .5ms (.25%) | .5ms (.25%)    | 199ms (99%) |

| 1% d        | uty cycle   | 99% duty cycle |             |

## And for test beam ...

#### When spill:

Full acquisition cycle

When no spill:

#### **IDLE MODE**

Duty factor = duty factor of the spill structure

# Consumption

- o The goal is 25μW/ch. (with Power Pulsing)

- The analogue part consumption :

is 2.3mW/Ch. Without Power Pulsing

ie 11.5µW with 99.5% Power Pulsing

- The ADC part comsumtion :

is 3.7mW/Ch. Without Power Pulsing

le 9.25μW/Ch. With 99.75% Power Pulsing

- Need to estimate digital part consumption

- → So far, on track

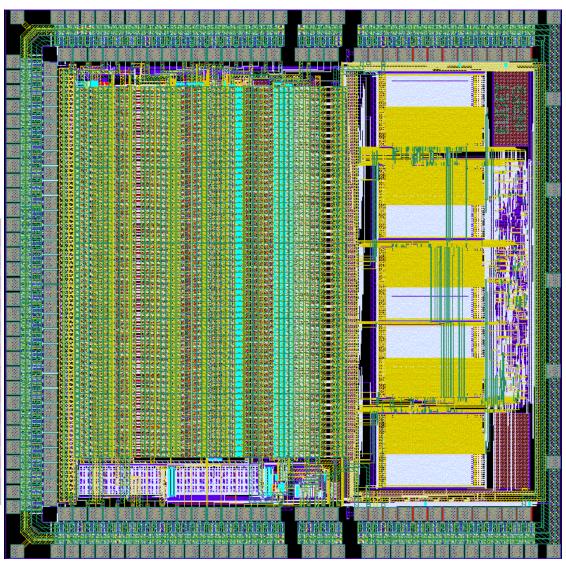

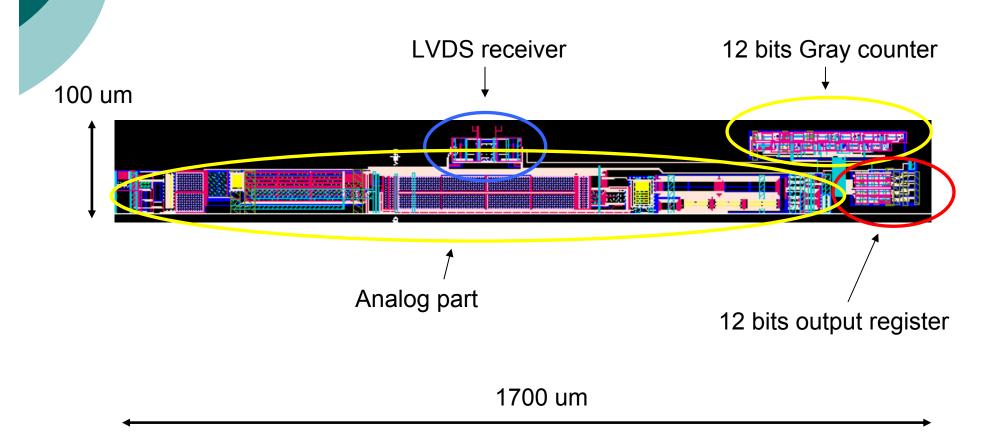

## Wilkinson ADC description

- Main characteristics

- Technology ams BiCMOS SiGe 0.35

- Fully differential structure (MC to MD input stage)

- 1V input dynamic range

- 12 bits output Gray code

- Counting frequency: 50MHz → 82µs conversion time

- Power supply: 3.5V (analog) and 2.5V (digital)

- Power consumption < 3mW</li>

- Circuit (1 channel) submitted in september

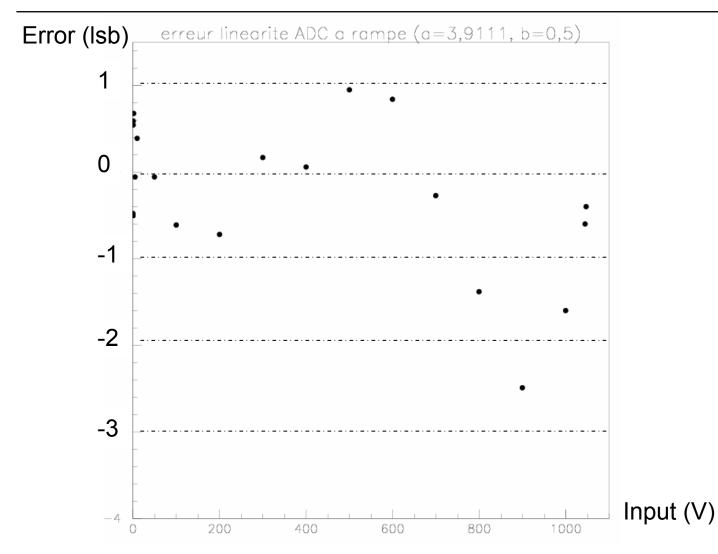

# Linearity error (simulation)

## Ramp ADC: layout (1 channel)

# ILC\_PHY5 schedule

- Analogue blocks :

- Designed

- Simulated

- Layouted

- Digital blocks :

- HaRD-ROC & MAROC2 as a starting point

- Many modifications to be done

- Wilkinson ADC: submitted (1 ch)

- Submission: November 24

## Conclusion

- Work is going on

- Complexity increases quickly

- Collaboration is very efficient and fruitful. It shall achieve the outstanding expectations within the very tight schedule

HaRD\_ROC (2006)

ILC\_PHY5 (2006)